�������ߣ����ݷ�

�༭����˼��

��Դ(yuan)��ӲAI

̨���������ν������(bu)�ϣ�������Ƚ��Ƴ̼۸����������λ���(ban)����

�����Ħ��ʿ����������һ(yi)�ݹ���̨����ı��棬��ϸ(xi)�ܽ���CoWos��PLP������3D SoIC�����½�չ��

o CoWos��װ��̨����Ԥ�ƣ���2026��(nian)�ף�ÿ�µ�CoWoS��Բ���ܽ��ﵽԼ6��Ƭ������ǰ��¶��2024��(nian)��CoWoS��װ���ܽ��ﵽ2.6-2.8��Ƭ/����ȣ�����һ(yi)���ࣻ

o ���(ban)����PLP����װ����(gai)���������(qi)�г�(chang)��ע�ġ����λ���(ban)����ء�Ŀǰ�����з��Σ����ģ(mo)��������(xu)��(shu)��(nian)ʱ�䣻

o 3D SoIC��װ��Ԥ�ƴ�2025��(nian)�°���(nian)��ʼ���Ӳ��ܣ�Rubin�ܹ������3D SoIC��װ������

o CoWos��װ��̨����Ԥ�ƣ���2026��(nian)�ף�ÿ�µ�CoWoS��Բ���ܽ��ﵽԼ6��Ƭ������ǰ��¶��2024��(nian)��CoWoS��װ���ܽ��ﵽ2.6-2.8��Ƭ/����ȣ�����һ(yi)���ࣻ

o ���(ban)����PLP����װ����(gai)���������(qi)�г�(chang)��ע�ġ����λ���(ban)����ء�Ŀǰ�����з��Σ����ģ(mo)��������(xu)��(shu)��(nian)ʱ�䣻

o 3D SoIC��װ��Ԥ�ƴ�2025��(nian)�°���(nian)��ʼ���Ӳ��ܣ�Rubin�ܹ������3D SoIC��װ������

������ļ������ֻ���(shang)��̨�����ʾ����2022��(nian)��2026��(nian)��CoWoS�����IJ���Ԥ�ƽ��Գ���60%����(nian)��������(chang)��Ѹ������(chang)����2026��(nian)�ף�ÿ�µ�CoWoS��Բ���ܽ��ﵽԼ6��Ƭ��

Ŀǰ��̨�����CoWoS�²���ԼΪ1.5��Ƭ��Ԥ�Ƶ�2024��(nian)�ף���һ(yi)��(shu)�ֽ�������ÿ��2.6-2.8��Ƭ��

ͬʱ��2024��(nian)ȫ��(nian)��̨����ƻ�Ͷ��280-320����Ԫ������Լ10%�������Ƚ���װ������

Ħ��ʿ��������ʦָ����ǿ���ķ�װ��(xu)��(qiu)����Ϊδ������(nian)̨����Ǿ�Բ�����(kuai)������(chang)����Ҫ��������

o Ԥ��2023-2026��(nian)��̨����Ǿ�Բ����ĸ�����(nian)����(chang)�ʣ�CAGR�����ﵽ31%��

o ��2023��(nian)���Ǿ�Բ��������ռ��̨�����������13%��

o Ԥ��2023-2026��(nian)��̨����Ǿ�Բ����ĸ�����(nian)����(chang)�ʣ�CAGR�����ﵽ31%��

o ��2023��(nian)���Ǿ�Բ��������ռ��̨�����������13%��

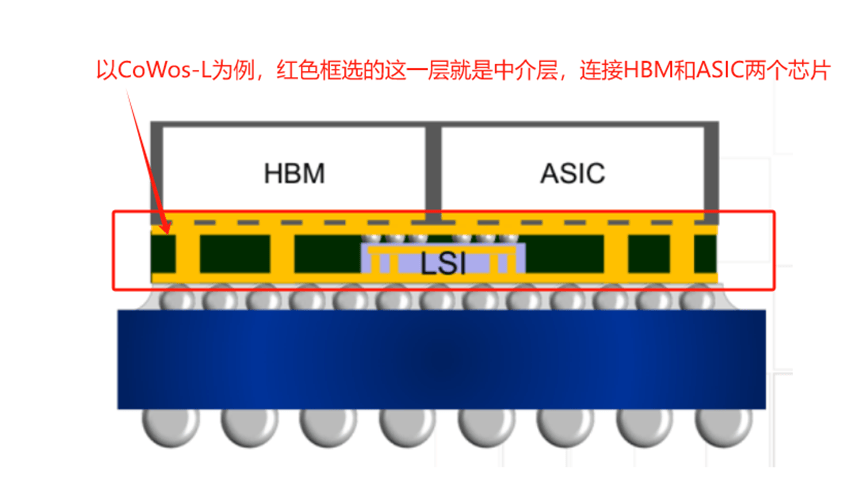

1��CoWoS-L��װ

СĦָ����̨�������ڼ�����CoWoS��������(kuo)չ���ص������ӦԽ(yue)��Խ(yue)��ߴ��AIоƬ��(xu)��(qiu)��(shang)���ر���CoWoS-L������

CoWoS��װ�����ַ�Ϊ����(zhong)���ͣ�CoWoS-S��CoWoS-R��CoWoS-L�����ǵ���Ҫ��(qu)�������н�����ƣ���������оƬ�Ĺؼ��㡣

�����˹�����оƬ�ߴ�����ӣ���ǰʹ�ù��н���CoWoS-S�����������������⡣

Ϊ��Ӧ��(dui)��һ(yi)��ս��̨�����Ƴ���CoWoS-L������������LSI+RDL�н�㣬��Ч����˴�ߴ�оƬ���������⡣

СĦԤ�ƣ�δ��̨������CoWoS�����ķ�չ����Ҫ��(ju)����CoWoS-L����Ӧ��(dui)������(kuo)���AIоƬ�����(xu)��(qiu)��

�������(ban)����PLP����װ����

СĦָ����̨�������ڽ������(ban)����PLP����װ�������о�(jiu)�������ģ(mo)��������(xu)Ҫ����(nian)ʱ�䡣

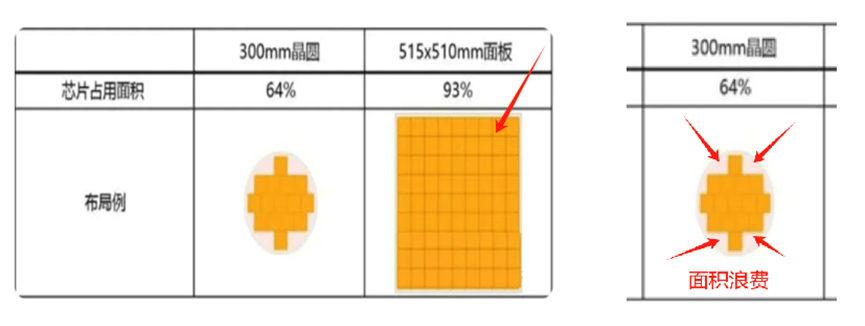

PLP��װ��һ(yi)��(zhong)���������������ڸ�(geng)��ľ������(ban)��(shang)�ķ�װ����������ͼ��ࣩ��

Ŀǰ��̨����ʹ�õ���Բ�ξ�Բ����(ban)�������������˷�(fei)������ͼ�Ҳࣩ��

�ݡ��վ����ޡ�����������AI�����ļ�����(xu)��(qiu)������̨��������̽��510�L �� 515�L�ľ��λ���(ban)��

���λ���(ban)����Ч�����Բ�ξ�Բ����������(shang)��������(xian)������̨���������������

Ȼ������Բ�λ���(ban)��ȣ����λ���(ban)���ڹ�̽�Ϳ����(bu)���Ⱥ�����(sui)�ѵ����⡣

СĦָ����Ҫʵ��PLP��װ�����Ĵ��ģ(mo)����������(xu)Ҫ��(shu)��(nian)ʱ��ļ������ء�

����3D SoIC�Ƚ���װ

3D SoIC��̨���翪�����Ƚ���װ������רע��ʵ�ָ��ܶȵ�оƬ��ֱ�ѵ������֮�£�CoWoS������Ҫ�Ǻ���ѵ�����

СĦָ����Ŀǰ3D SoIC�������г�(chang)��(shang)�����(dui)��ΪС�ڣ�ֻ��AMD����Ryzen 3D��MI300 AI�������в��á�

Ԥ�ƴ�2025��(nian)�°���(nian)��ʼ��̨���罫��(zhu)������3D SoIC�IJ��ܡ���2025��(nian)�ף�Ԥ��ÿ�µ�3D SoIC���ܽ��ﵽ��Լ12,000��14,000Ƭ��Բ����2026��(nian)�ף�Ԥ�ƽ�����ÿ��20,000Ƭ��Բ��

���⣬СĦ�Ʋ⣬Ӣΰ���Rubin�ܹ��Լ�ƻ����M5���������ܻ����3D SoIC������